- 您现在的位置:买卖IC网 > Sheet目录1995 > HI1175JCB-T (Intersil)CONV A/D 8BIT 20MSPS 24-SOIC

11

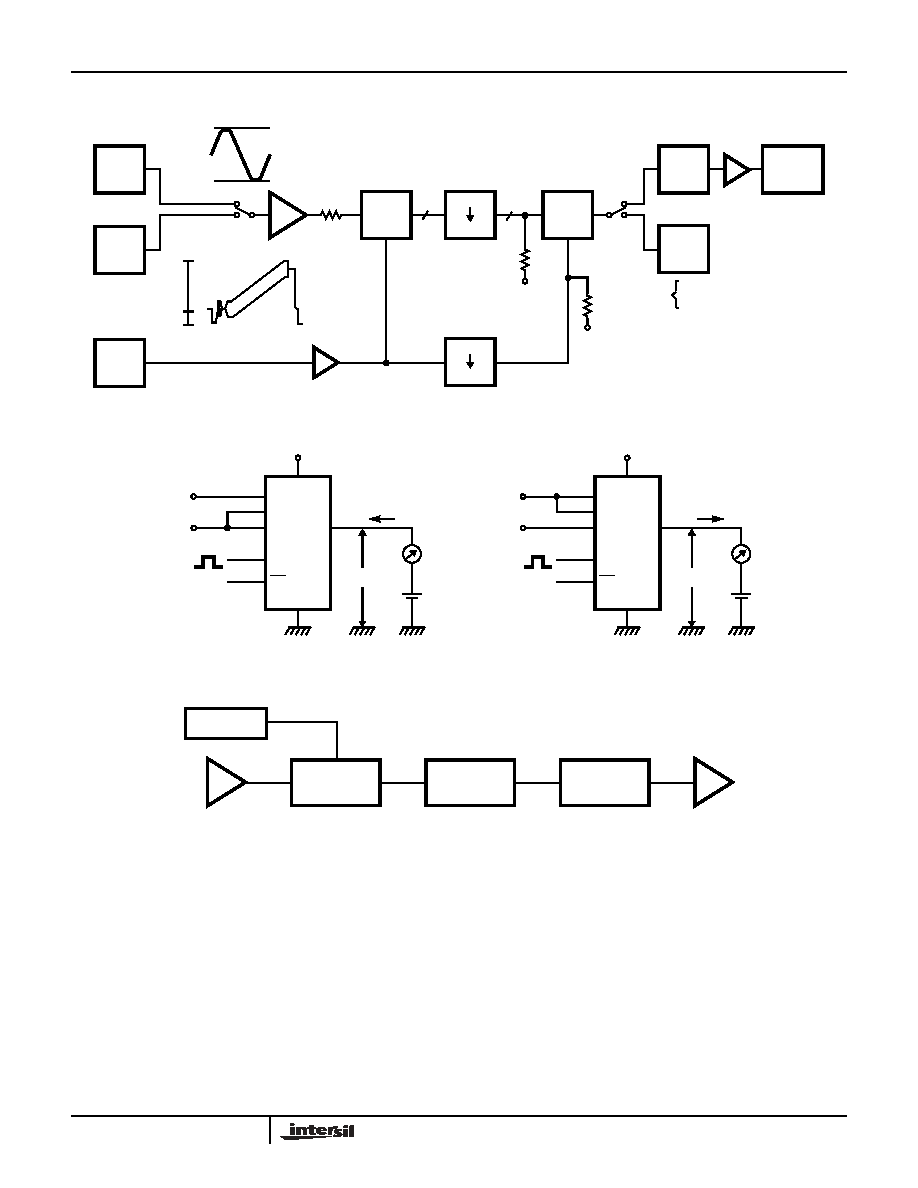

FIGURE 22. MAXIMUM OPERATIONAL SPEED AND DIFFERENTIAL GAIN AND PHASE ERROR TEST CIRCUIT

FIGURE 23. DIGITAL OUTPUT CURRENT TEST CIRCUIT

HA5020 (Single)

HA5022(Dual)

HA5024 (Quad)

HA5013 (Triple)

HI1175 (8-Bit)

HSP9501

HSP48901

HSP43881

HSP43168

HI3338 (8-Bit)

HI1171 (8-Bit)

HA5020 (Single)

HSP9501: Programmable Data Buffer

HSP48901: 3 x 3 Image Filter, 30MHz, 8-Bit

HSP43881: Digital Filter, 30MHz, 1-D and 2-D FIR Filters

HSP43168: Dual FIR Filter, 10-Bit, 33MHz/45MHz

CMOS Logic Available in HC, HCT, AC, ACT and FCT.

HA5013: Triple, 125MHz, IOUT = 20mA

HA5020: Single, 100MHz, IOUT = 30mA, Output Enable/Disable

HA5022: Dual, 125MHz, IOUT = 20mA, Output Enable/Disable

HA5024: Quad, 125MHz, IOUT = 20mA, Output Enable/Disable

FIGURE 24. 8-BIT SYSTEM COMPONENTS

Test Circuits (Continued)

SIGNAL

SOURCE

NTSC

SG

VIN

8

SCOPE

VECTOR

620

DG

ERROR RATE

SG

(CW)

AMP

HI1175

DUT

ECL

TTL

D/A

10-BIT

-5.2V

CLK

1

2

1

2

HPF

COUNTER

DP

620

-5.2V

ECL

TTL

fC

-40

0

100

IRE

SYNC

BURST

0.6V

2.6V

40 IRE

MODULATION

0.6V

2.6V

fC -1kHz

HI20201

VRT

VIN

VRB

CLK

OE

GND

VDD

0.6V

2.6V

VOL

IOL

+

-

VRT

VIN

VRB

CLK

OE

GND

VDD

0.6V

2.6V

VOH

IOH

+

-

HI1175

A/D

D/A

DSP/

P

REFERENCE

ICL8069

AMP

HI1175

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HI1178JCQ

CONV D/A 8BIT TRPL 40MHZ 48-PQFP

HI3-674AKN-5

IC ADC 12BIT 67KSPS 28-SBDIP

HI3-7159A-5Z

IC ADC 5-1/2 DIGIT 28-PDIP

HI3-DAC80V-5

CONV D/A 12BIT OUTPUT AMP 24PDIP

HI3026JCQ

ADC FLASH 8BIT 120MSPS 48-PQFP

HI3338KIBZ

IC DAC 8BIT CMOS 16-SOIC

HI5628INZ

IC DAC 8BIT 125MSPS DUAL 48-LQFP

HI5660IBZ

CONV D/A 8-BIT 125MSPS 28-SOIC

相关代理商/技术参数

HI1175JCP

制造商:Harris Corporation 功能描述:

HI1176

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:8-Bit, 20 MSPS, Flash A/D Converter

HI1176_05

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:8-Bit, 20 MSPS, Flash A/D Converter

HI1176-EV

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:8-Bit, 20 MSPS, Flash A/D Converter

HI1176JCQ

制造商:Rochester Electronics LLC 功能描述:32 PQFP INDTEMP VIDEO A/D 8 BIT 20MSPS SYNC-CLAMP V-REF - Bulk

HI1176JCQ-T

制造商:Rochester Electronics LLC 功能描述:- Bulk

HI1177

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:8-Bit, 40MSPS, 2-Channel D/A Converter

HI1177JCQ

制造商:Rochester Electronics LLC 功能描述:32 PQFP INDTEMP DUAL VIDEO D/A 8BIT 40MHZ - Bulk 制造商:Harris Corporation 功能描述: